シリアル通信で Hello Fpga 1 Acri Blog

実習1 シフトレジスタの設計 以下のshiftregistervで設計される回路を実習ボードの実装して、その動作を確かめること。 ただし、toplevel entity はshiftregister とする。 入出力の割り当ては表のとおりにすること。回路記述⾔語VerilogHDL 実験第⼀J2課題 1 佐藤証⻄9613 akashisatoh@uecacjp

Verilog シフトレジスタ 記述

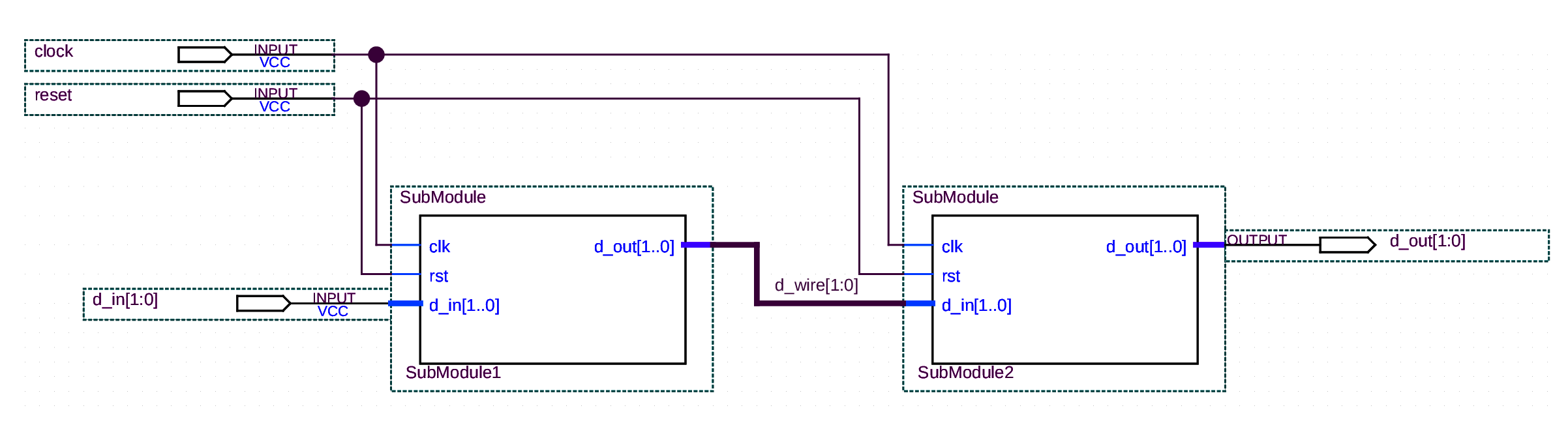

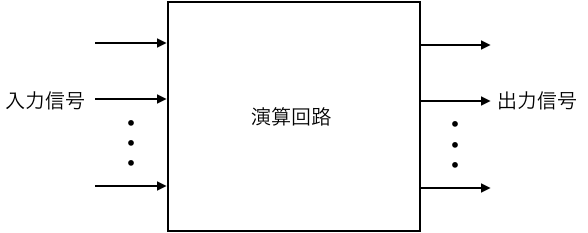

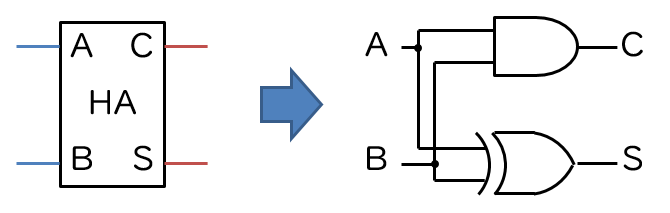

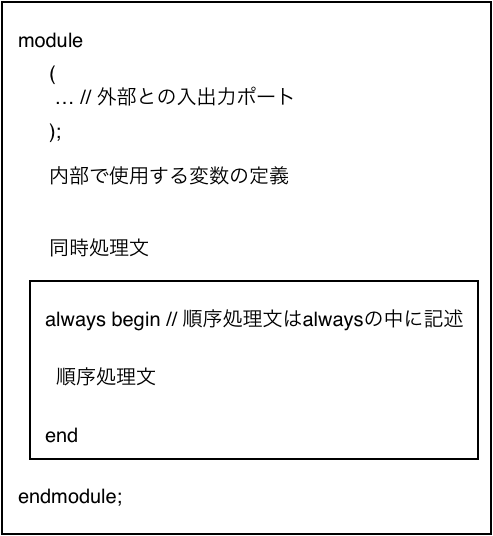

Verilog シフトレジスタ 記述- はじめに、Verilog HDLの記述スタイルについて解説します。 Verilog HDLでは回路をモジュール(module)単位で構成します。つまり、問題1では、図1のように回路を"モジュール"の枠に収めて定義します。そして、モジュールに接続する信号を"ポート"とし 問題1 以下の回路をVerilog HDLで記述してください 答え. 解答はこちら (←クリック) 「完全マスター! 電子回路ドリル III」バックナンバー 電子回路マスターへの道 ~栄光のゴール~ Verilog HDLの記述スタイル ~3学期期末考査~ HDLマスターへの

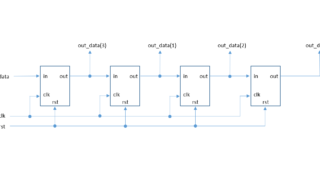

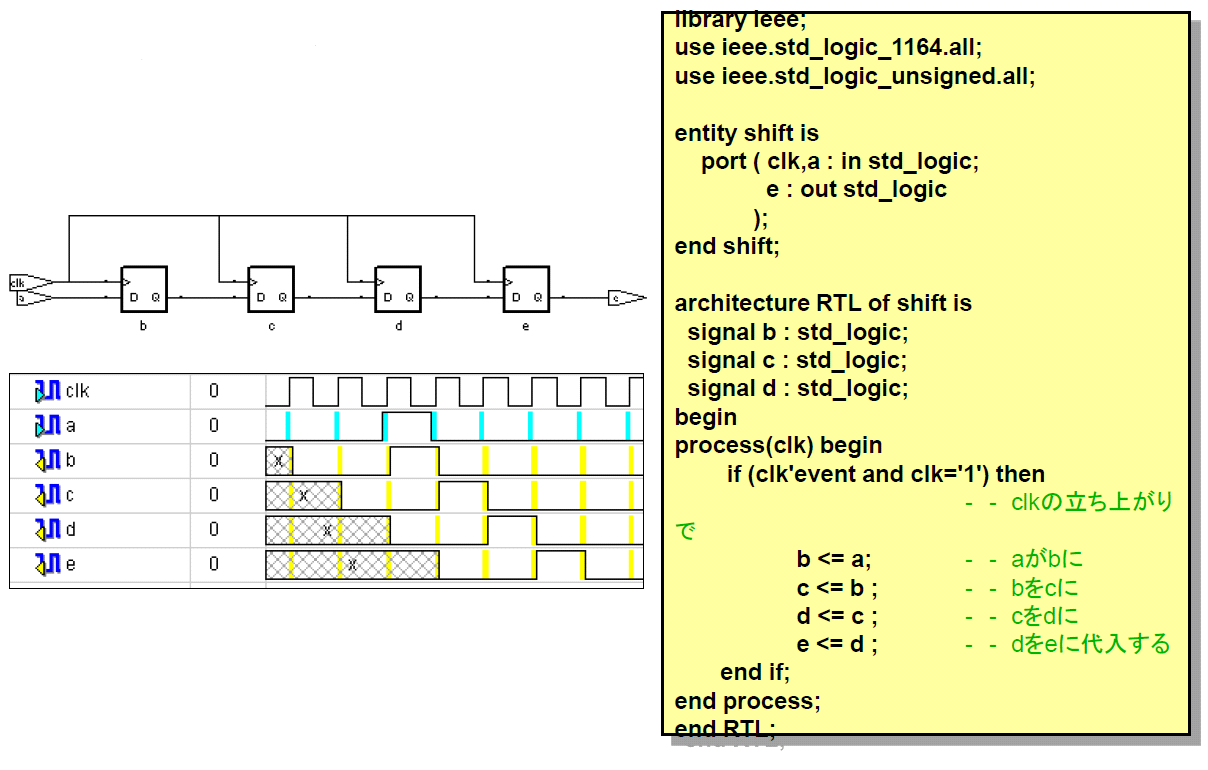

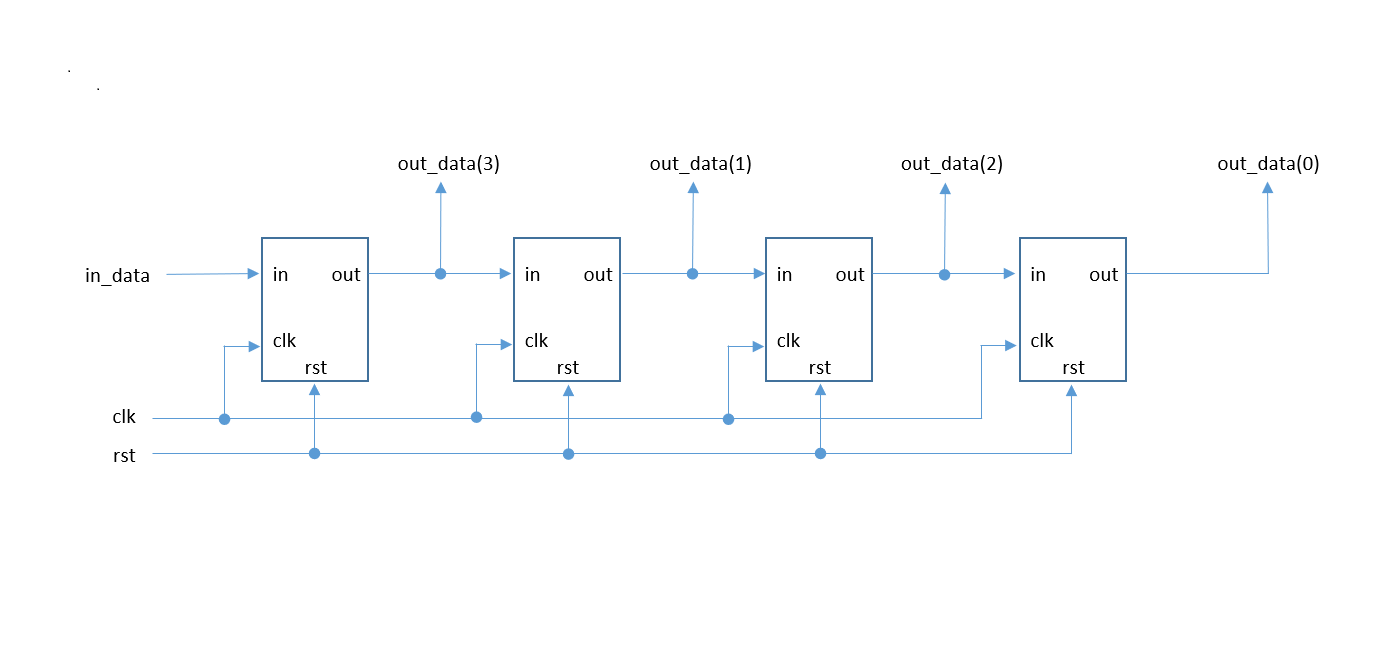

シフトレジスタの回路図と記述法 Verilog Vhdl 組み込みエンジニアのメモ帳

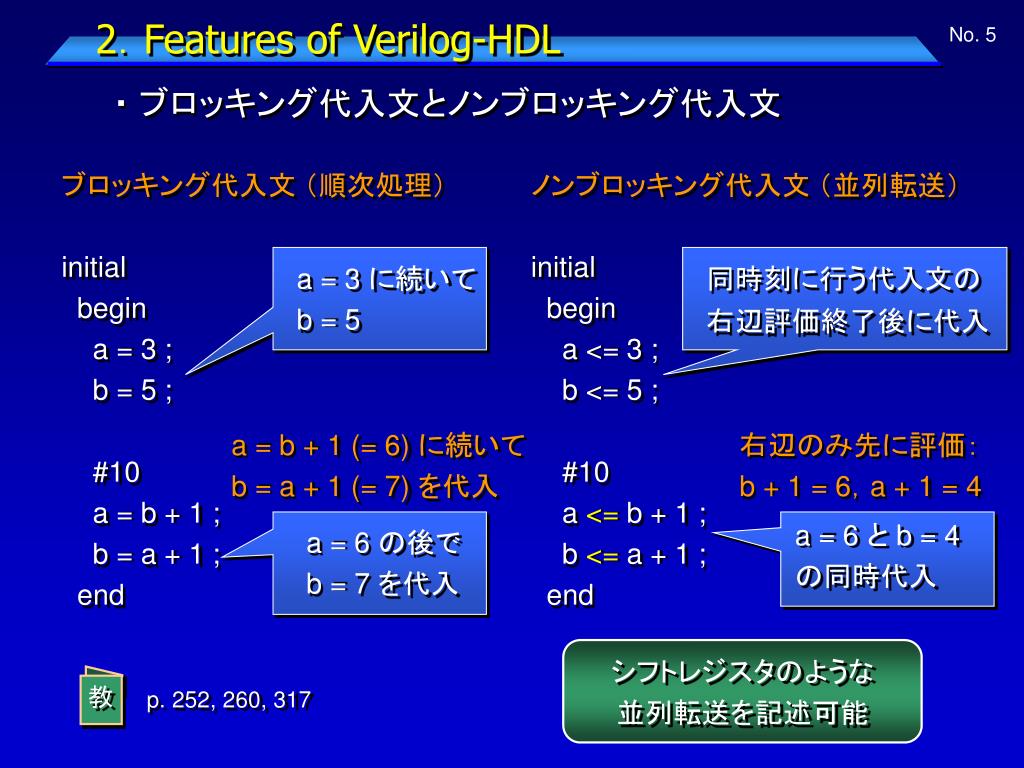

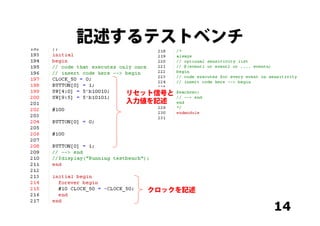

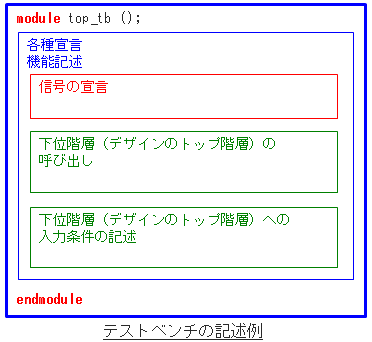

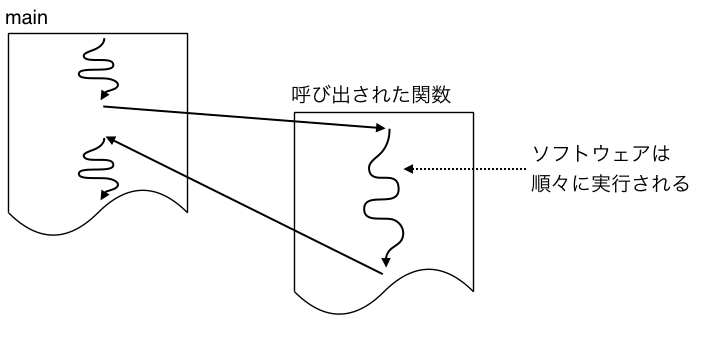

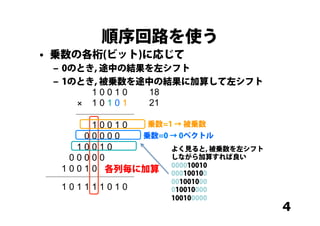

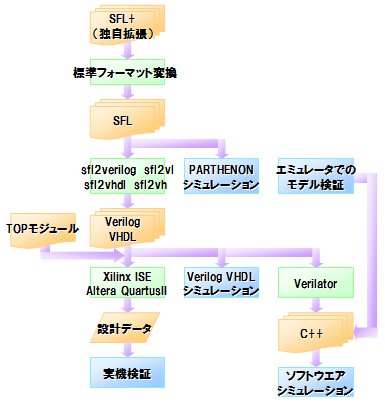

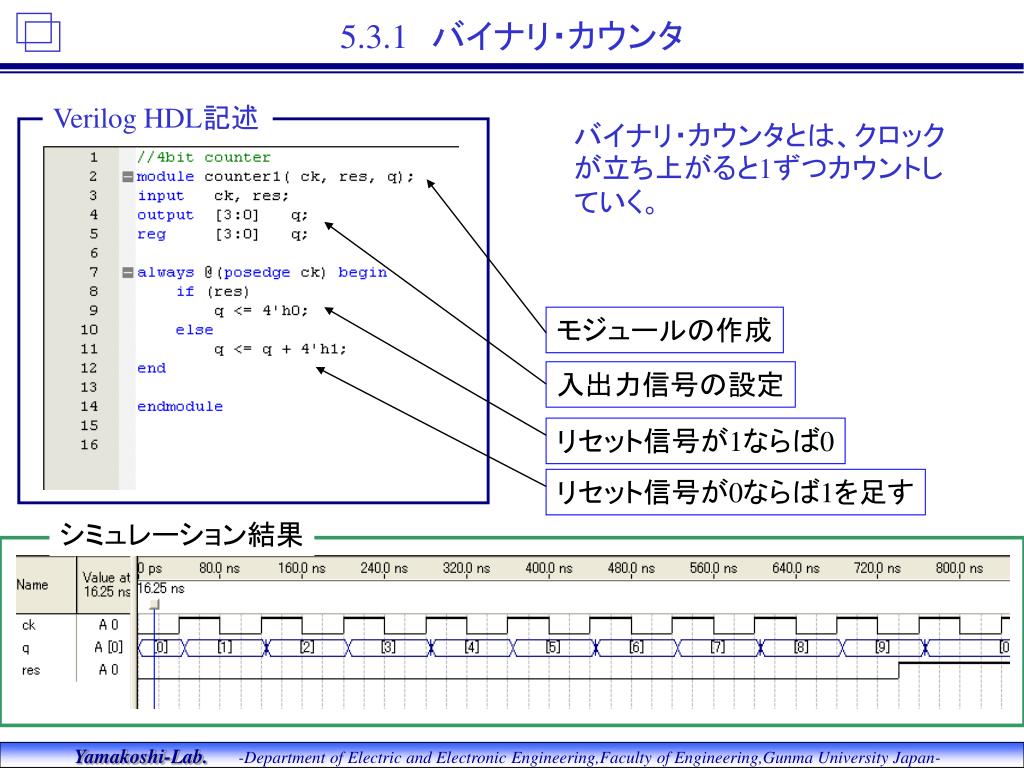

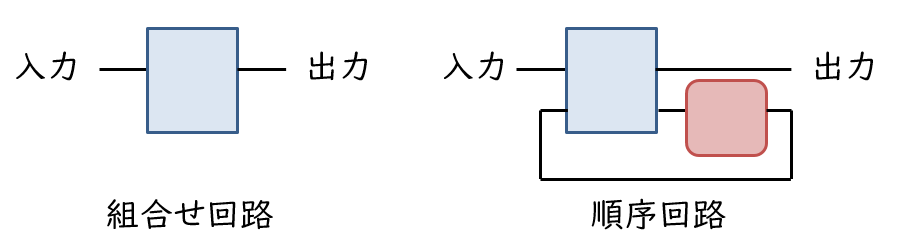

Web版 VerilogHDL入門 4 シミュレーション記述 設計した回路が正しく動作するかの検証の為に実装する前にコンピュータ上でシミュレータを動作させてシミュレーションを行います。 シミュレーションは大別して論理シミュレーションと遅延 Verilogalways文は順序回路として記述すべし! 記述を5つに分解して解説します! 本記事では、always文の記述構成や注意点をわかりやすく説明します。 always文の要点 reg宣言とセットで使用代入記号は「 verilog で順序記述である case 文が論理合成では並行として扱われる、というのはそのような取り決めが存在するのでしょうか? それとも、そのように扱う回路合成ソフトが多いというような経験的なものなのでしょうか?

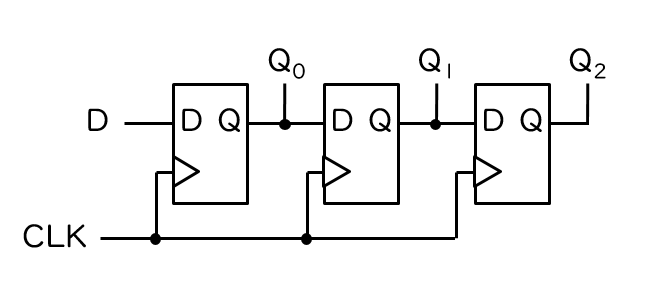

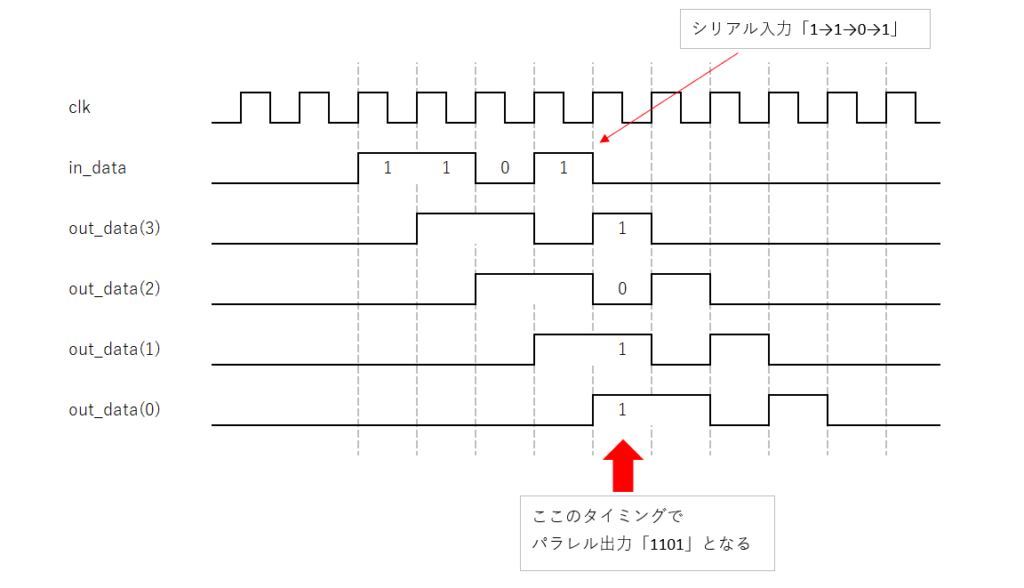

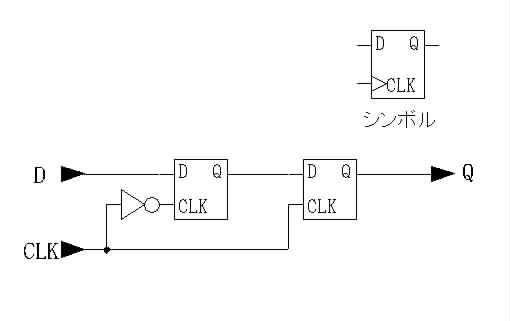

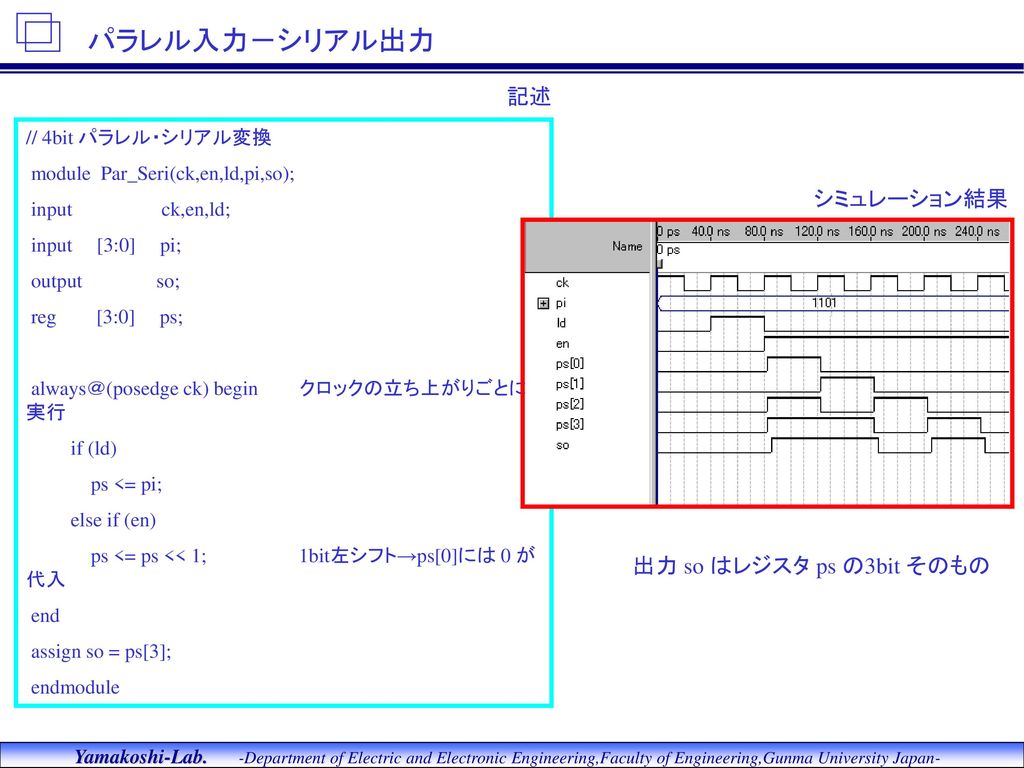

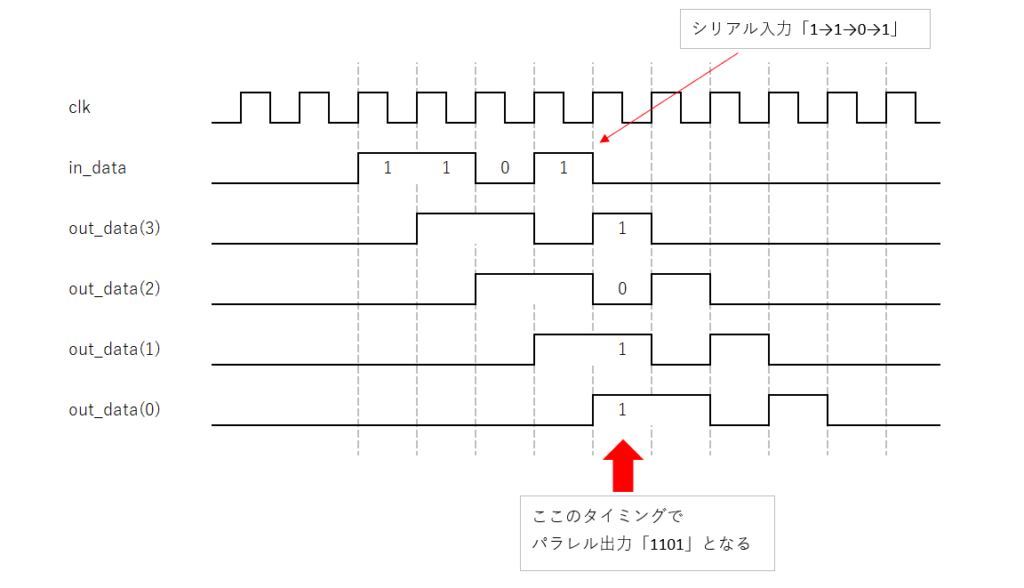

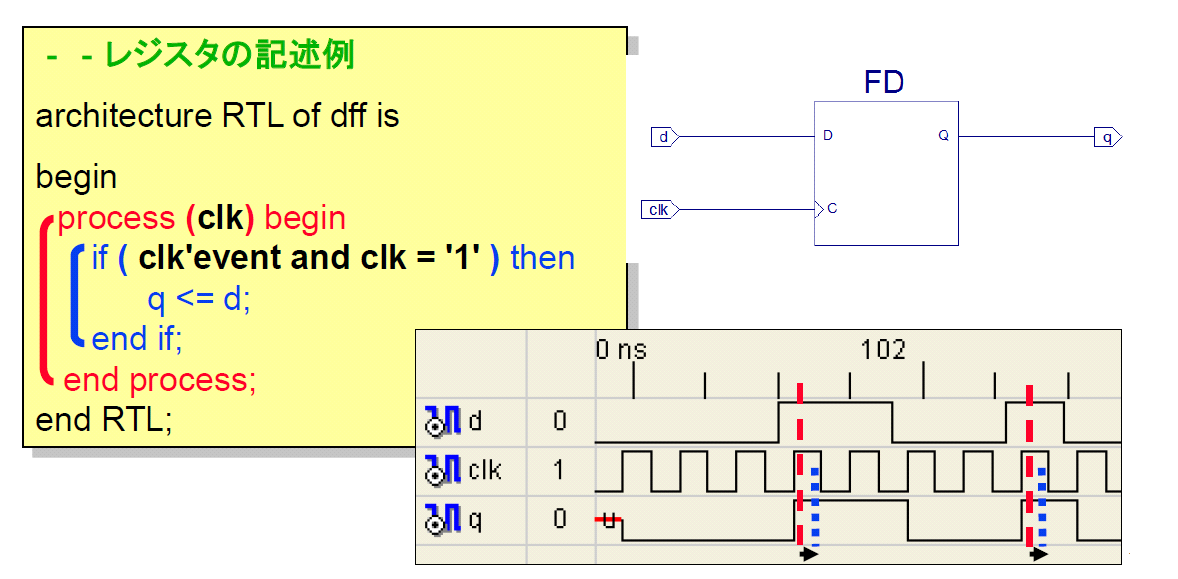

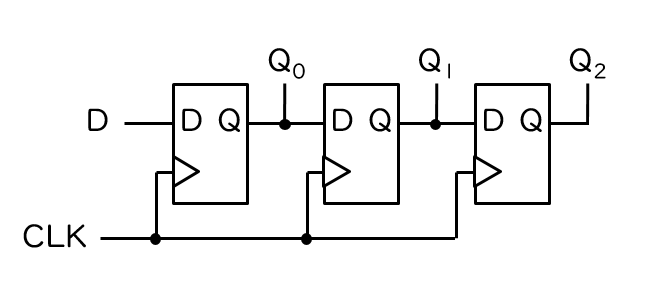

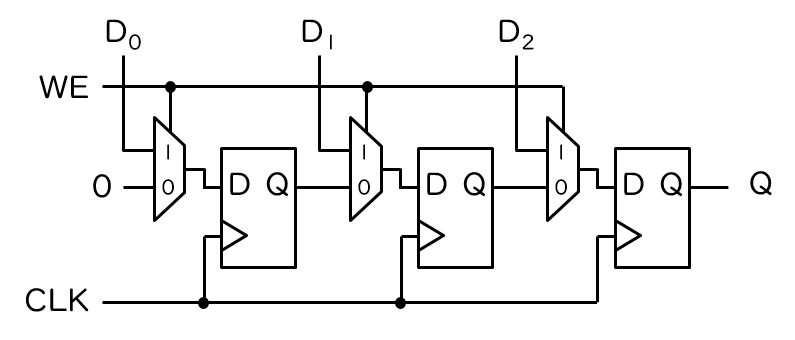

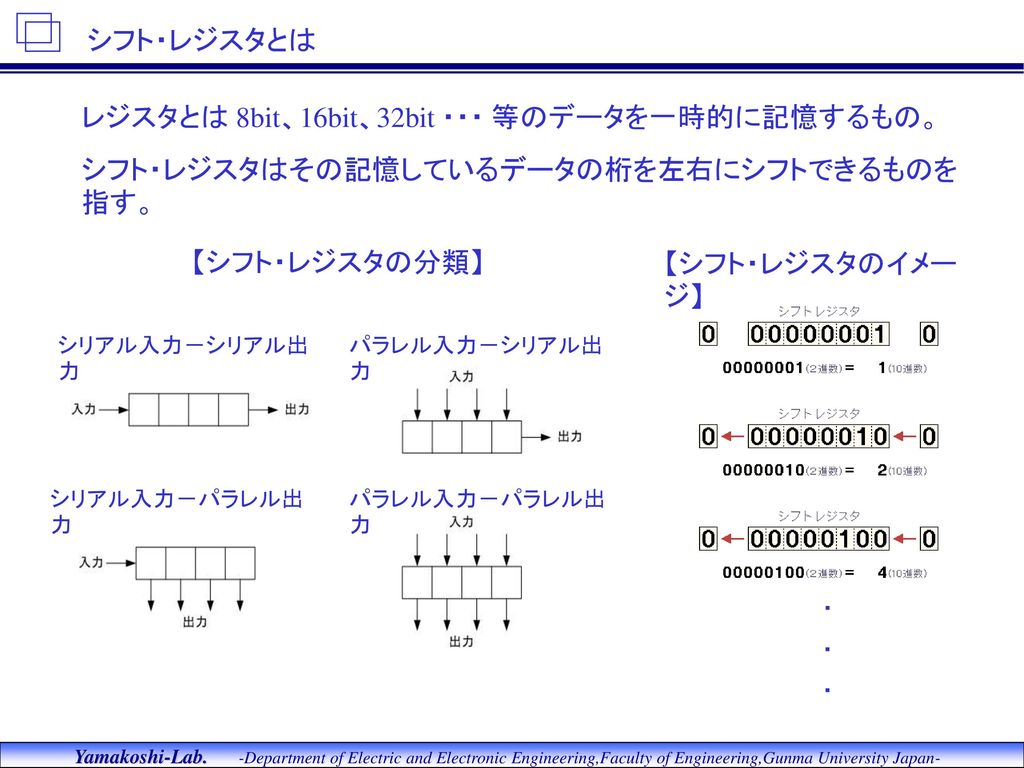

VerilogHDL で論理回路を記述したら、実機確認する前にシミュレーションで検証 シフト演算子は、各ビットの値を左や右にシフトさせます。 左シフトは MSB 側にシフトされ、LSB 側には 0 が補充されます。 宣言部には、ポート宣言やレジスタ宣言 シフトレジスタの回路図と記述法 (verilog, VHDL) まずシフトレジスタとは、FF (フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。 よく使われる場面として、直列並列変換 (シリアルパラレル変換)があるかなと思います32 記憶素子を使った回路 順序回路記述の前に記憶素子を使用した回路記述を説明します。 ここでは、記憶素子としてDタイプ・フリップフロップ (DFF)を想定します。 他のタイプの素子については参考文献を参照してください。 DFFは単ゲートよりも機能が

Verilog シフトレジスタ 記述のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

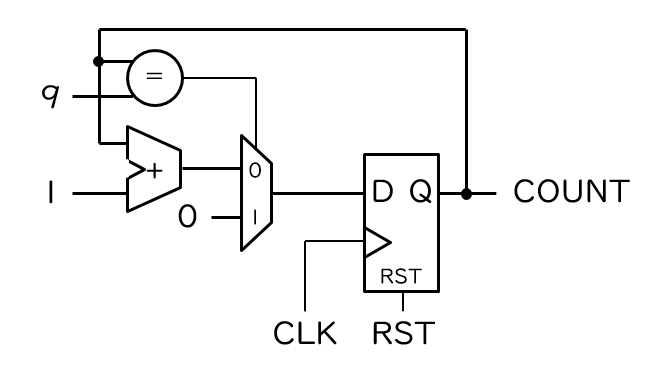

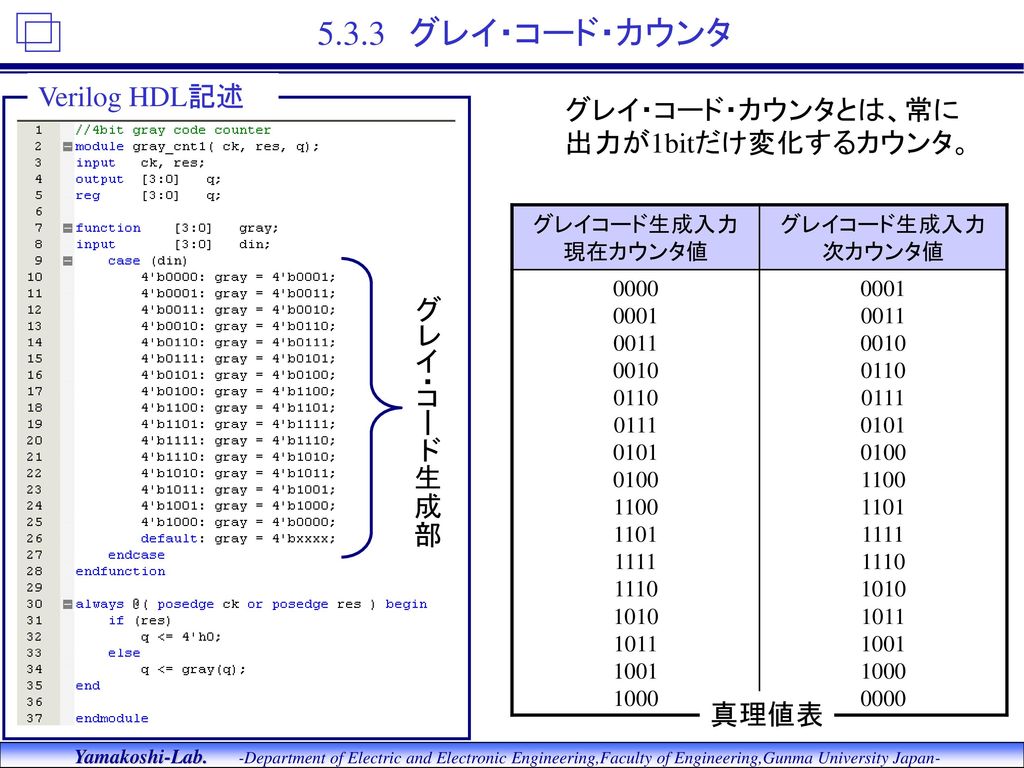

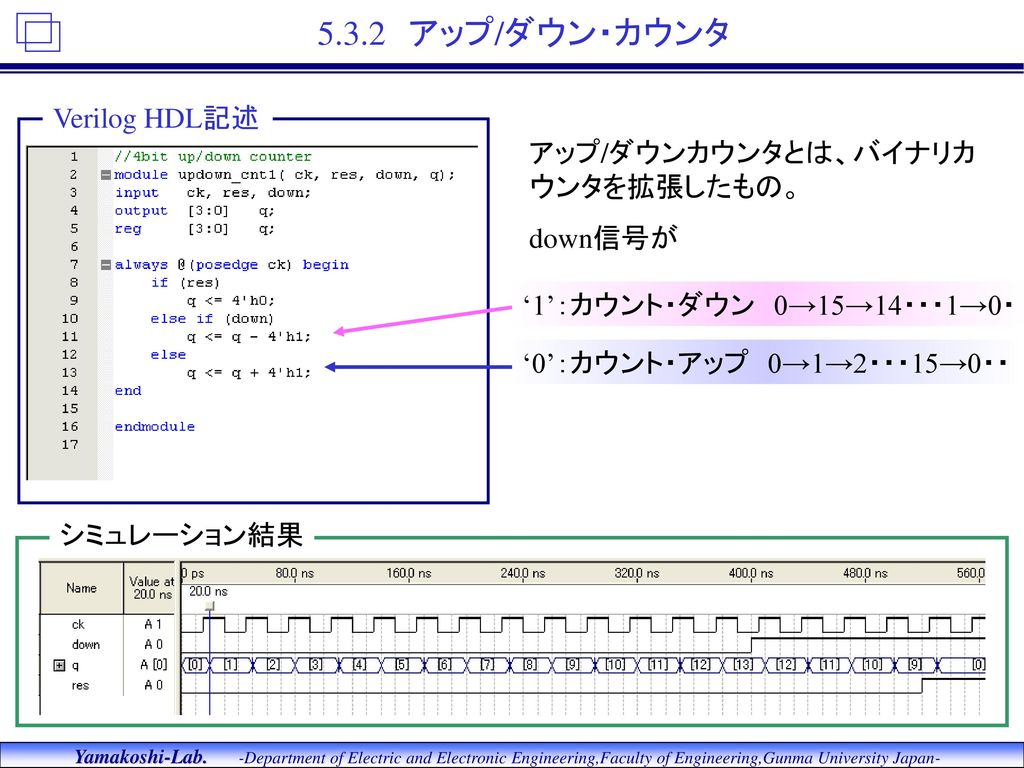

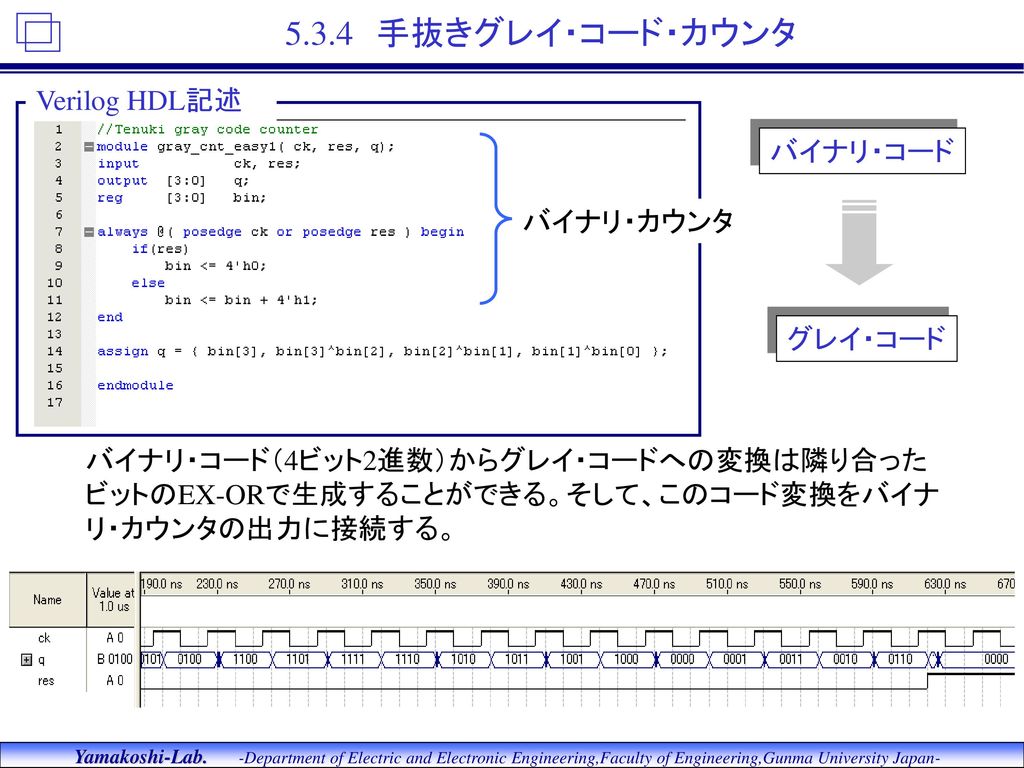

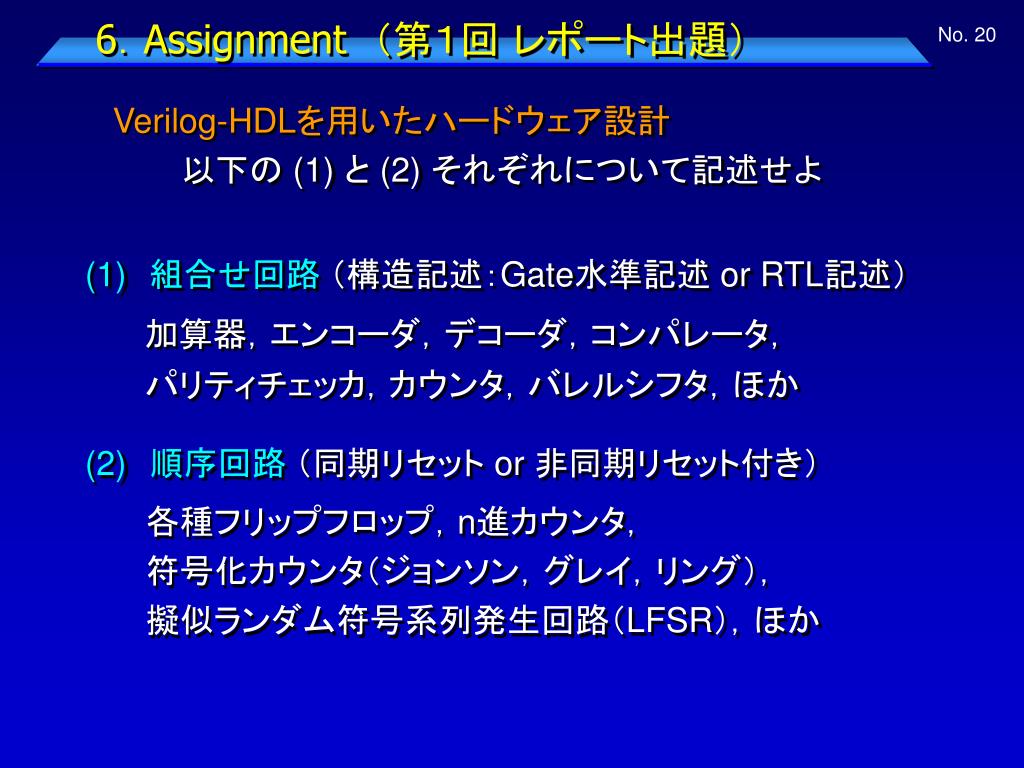

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |  5 3 各種カウンタ 平木 Ppt Download |

「Verilog シフトレジスタ 記述」の画像ギャラリー、詳細は各画像をクリックしてください。

5 3 各種カウンタ 平木 Ppt Download | 5 3 各種カウンタ 平木 Ppt Download |

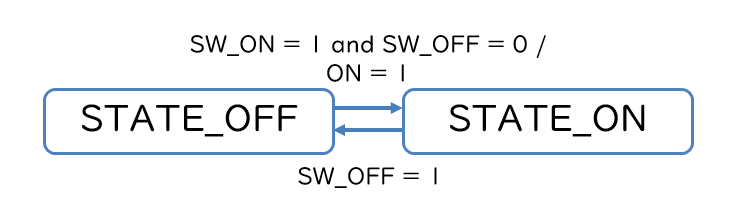

チャタリング除去回路を記述してみる FPGAボードを使っているとスイッチをよく使う。 スイッチを押すとノイズ(チャタリング)が起こる。 というわけで、色々と参考にしてチャタリング除去回路を書いたのでメモしておく。 Verilogのデータ型として主に用いるのはwire (ネット型)とreg (レジスタ型)です。 wireは配線に対応し組み合わせ回路の記述に使えますが、regは記述の仕方によって組み合わせ回路になったり順序回路であるFFやラッチになったりします。 文法的には wire assign

Incoming Term: verilog シフトレジスタ 記述,

0 件のコメント:

コメントを投稿